#### Th<sub>2</sub>F-3

# Post-Process Local Porous Silicon Integration Method for RF Application

G. Scheen<sup>1,2</sup>, R. Tuyaerts<sup>1</sup>, M. Rack<sup>1</sup>,

L. Nyssens<sup>1</sup>, J. Rasson<sup>1</sup>, and J.-P. Raskin<sup>1</sup>

### Synopsis

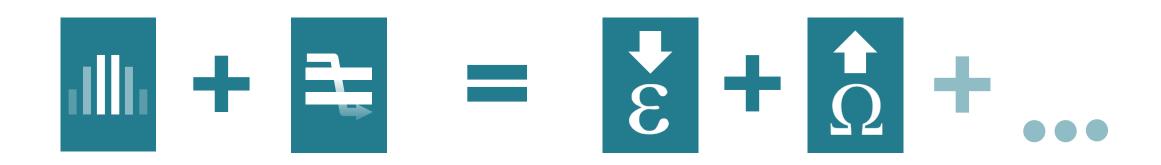

Why?

How?

What?

Porous silicon for

### Strategic choice for RF applications

### **Co-integration**

Digital/Analog and RF FEM

# Silicon still interesting?

Excellent control

of Si process

Low production cost

of the substrate

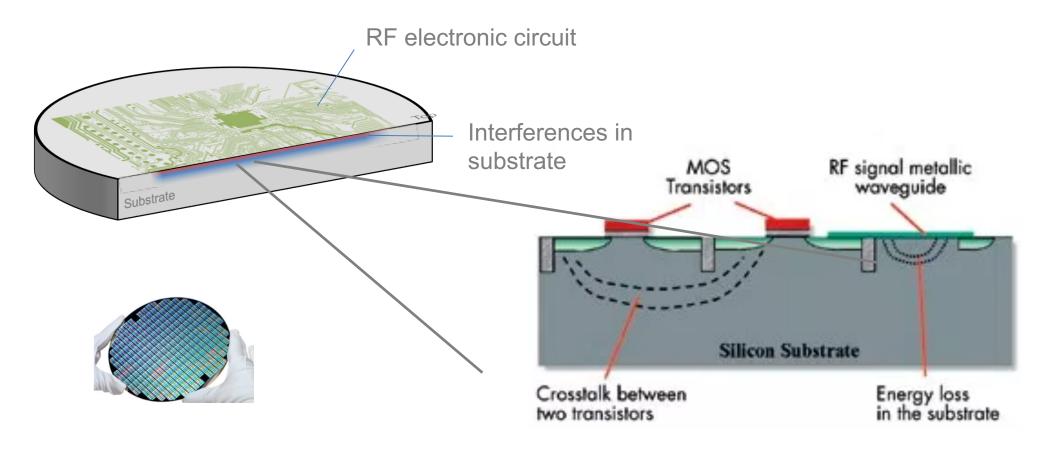

#### Silicon Substrate

# Only mechanical support?

High resistivity

Silicon-on-Insulator

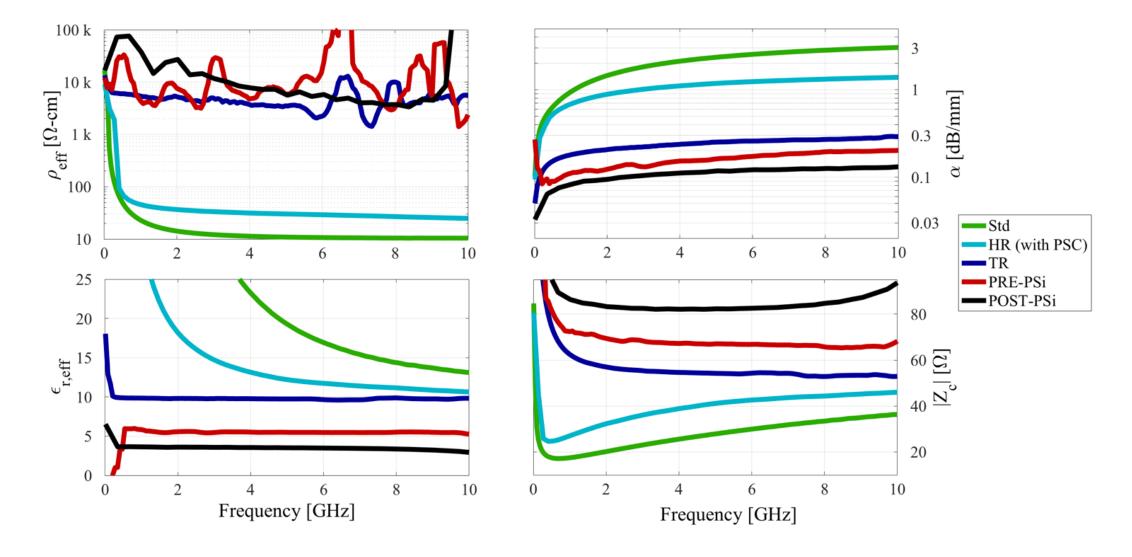

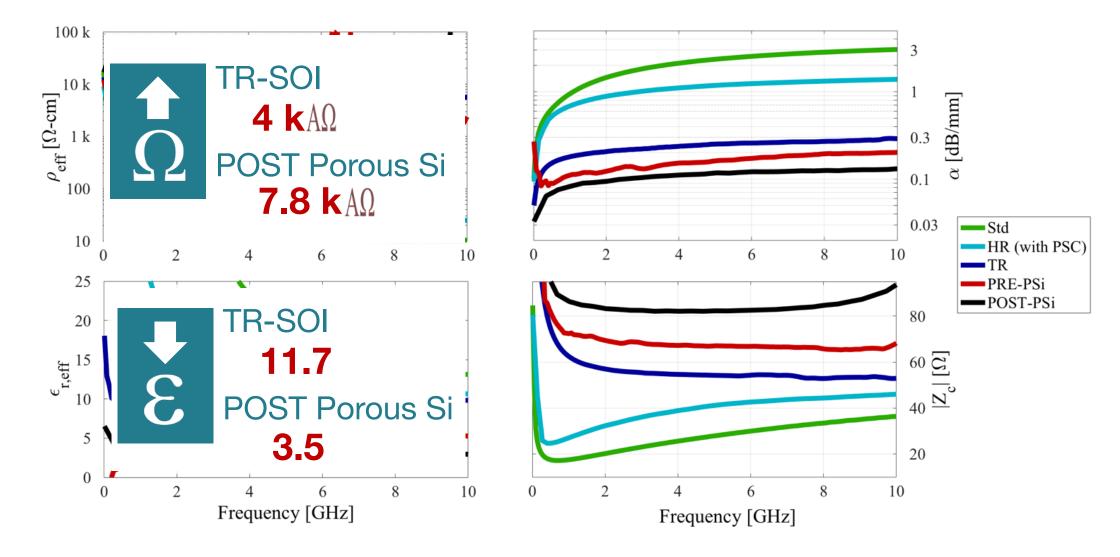

Trap-rich HR-SOI Benchmark

## RF silicon substrate history

High Linearity

Level

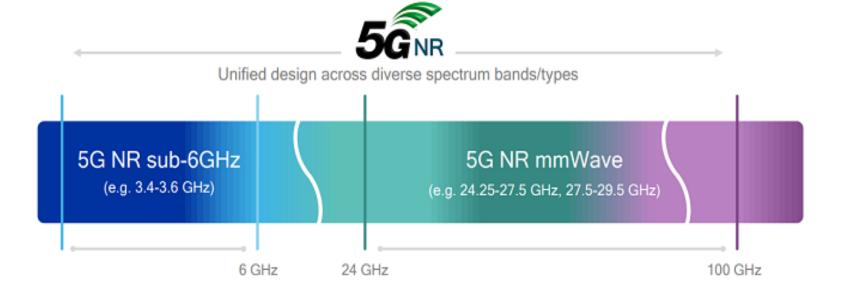

Source: Qualcomm

Silicon, the Substrate for 5G?

Silicon, the Substrate for 5G?

## Trap-rich HR-SOI

Silicon, the Substrate for 5G?

# How can we reduce the permittivity of silicon?

The question ...

## Porous Silicon, the solution?

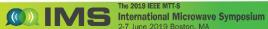

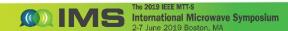

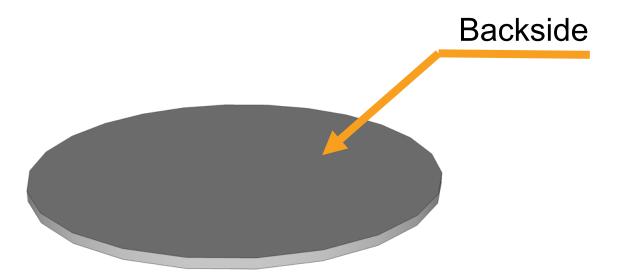

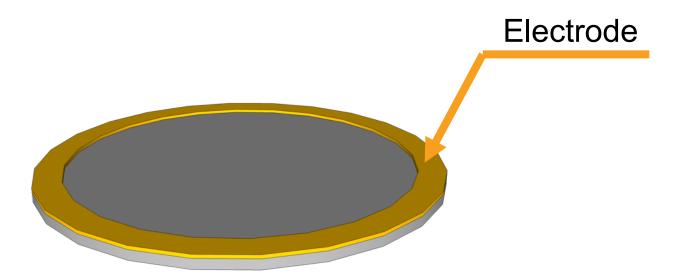

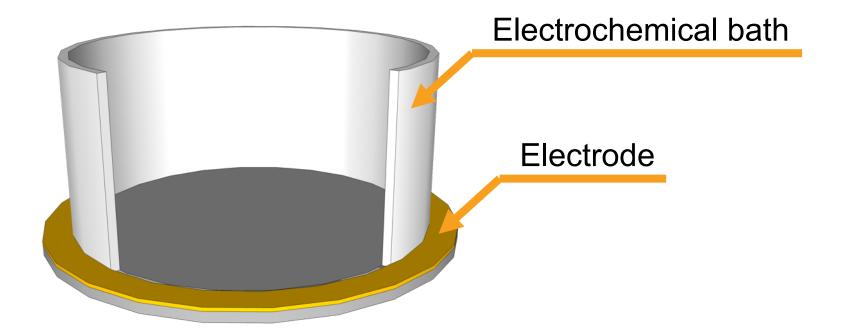

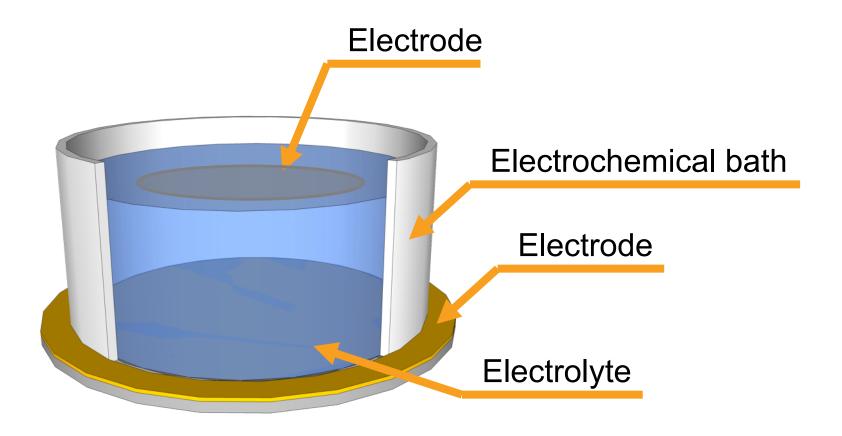

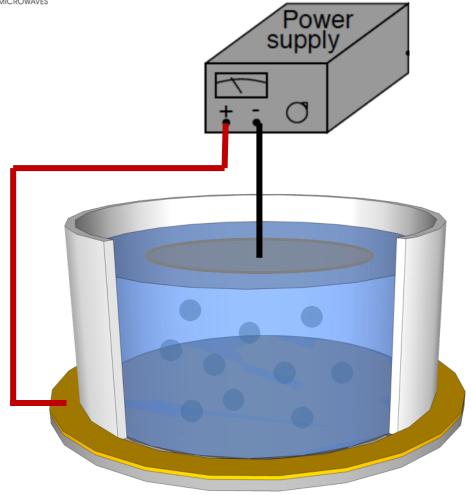

#### F ions in electrolyte

$$Si + 6 F^{-} + 2 H^{+} + 2 h^{+} \rightarrow SiF_{6}^{2-} + H_{2}$$

Holes in Silicon

Holes attracted by peak effect.

Etching at the tip.

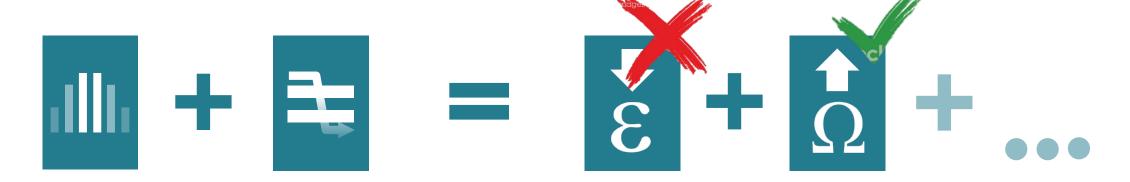

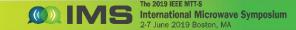

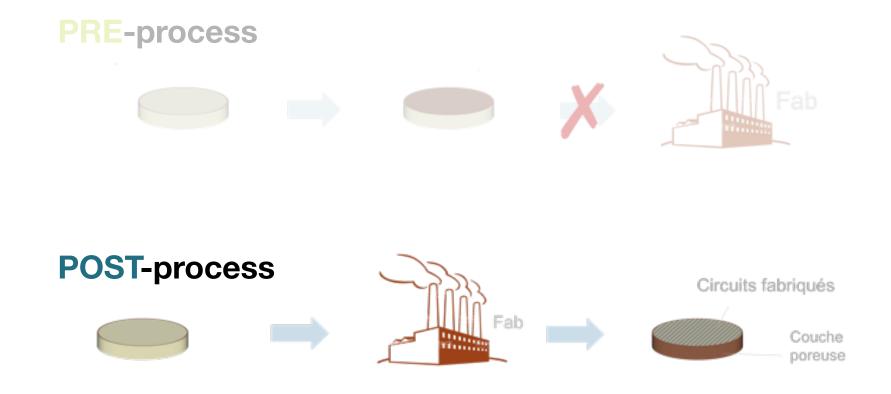

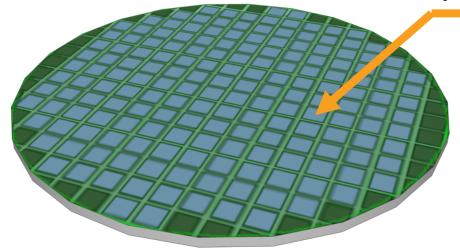

Porous silicon is produced before the foundry steps

## Usual approach

# Strongly CMOSIncompatible

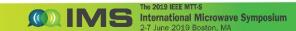

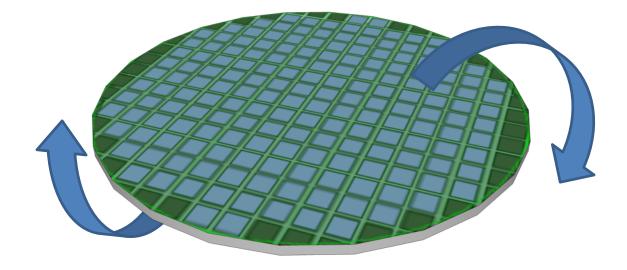

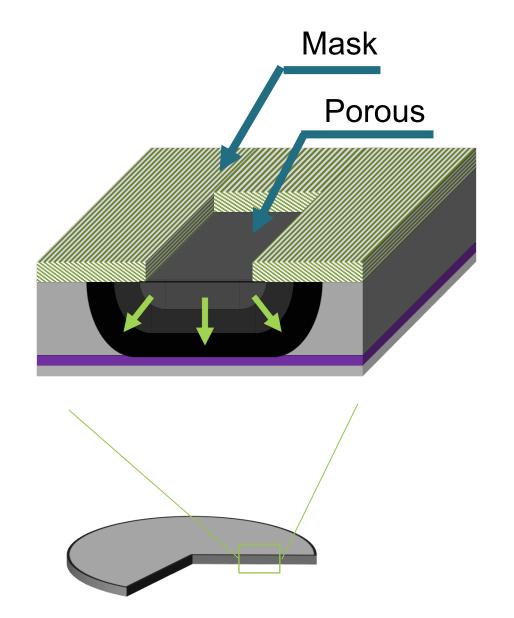

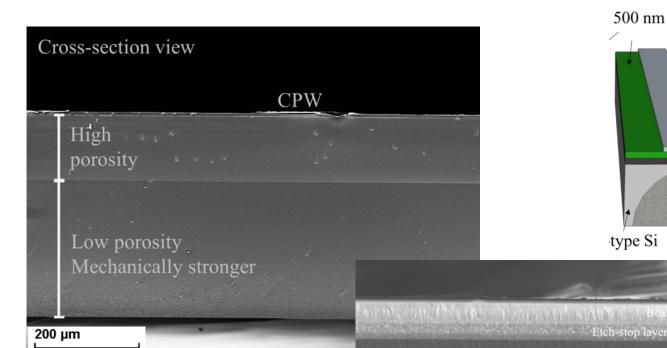

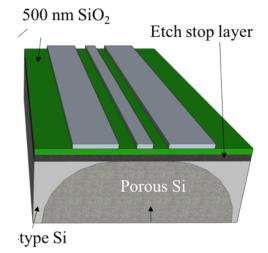

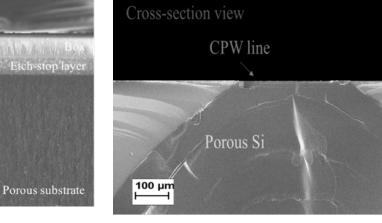

## Innovative approach

#### Processed substrate

# Post-process norous silicon

porous silicon Technology

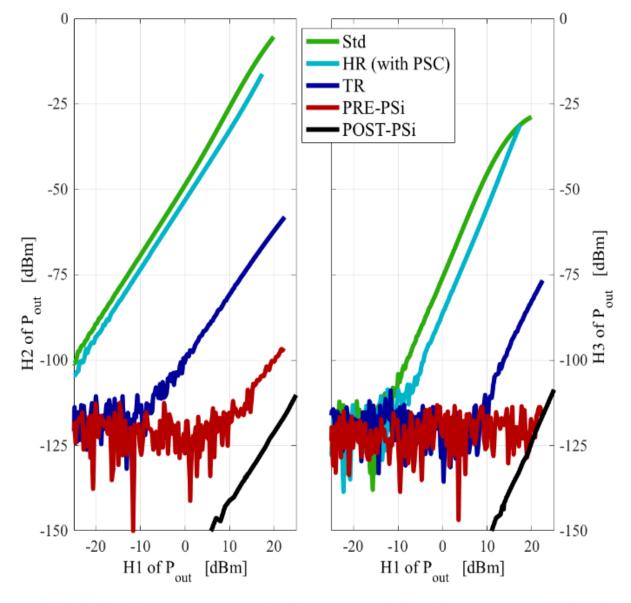

### Linearity

TR-SOI

-75 dBm

**POST Porous Si**

-130 dBm

### Conclusions

**High Performances**

**CMOS-** compatible

Somethingon-porous silicon

**Great flexibility**